在模拟信号链中经常用到负电源以处理负信号,同时也有正电源轨。但是从直流单电源得到正负双电源是不如使用交流电得到双电源那般容易的。TODO:这句话也挪到下面这篇文章里面开头。得到正负双电源在小功率电源中有几种方法来实现,见另一篇文章【正负电源方案简介】。这篇文章则详细介绍一个SEPIC+Ćuk组合拓扑来实现的正负电源的设计和制作测试。

拓扑简介

SEPIC

Ćuk

有空再说吧。看参考资料

原则上来说,由于输入电感的存在,sepic和cuk都属于输入电流连续的拓扑,对于输入的影响相对较小。 不过实际上则要看设计。

选型和参数计算

DC-DC芯片选型

这里使用SEPIC作为主输出,因此可以选用Boost控制器或者Boost转换器来完成这个要求,可以直接使用非同步整流Boost芯片。

MOS 耐压 输入+输出+余量

电流 输入+输出+纹波电流

输入耐压

输出

占空比要求

为了设计简单,同时这里设计要求不高,因此选用的DCDC芯片为MT3608或者SX1308,两者虽然厂家不同但是丝印一致,手册几乎一致。选用这个主要是因为便宜,只要三毛。

这个芯片的开关限流标称为设计上4A,不过按照国产IC的尿性,这个大概是达不到,而且SOT23-6的热阻太大,同类封装很少又标称大电流的。SW最大电压30V.

实际第一版测试中选用的是MT3608L,开关限流为2.5A,手册上标注为经过测试保证而非前面的理论值。SW最大电压22V.

CCM模式下,占空比为:

电感

二极管

耦合电容

SEPIC侧的耦合电容只需要承受输入电压的直流,以及纹波电压。 Cuk测的耦合电容则需要承受输入+输出电压的直流,以及纹波电压。 因此除了耐压的考量还需要考虑直流偏压下电容容量的下降。

耦合电容容量,使其纹波电压不超过输入电压的5%。

保守估计即使占空比100%,1Mhz频率下只需要20uF. 这里占空比为71.4%,14uF即可。考虑到电容的压降,大概三个22uF 25V 1206 或者 5个0805.。。。 2.594 GRM21BR61E226ME44 0805 5.000uF GRM31CC71E226ME15 1206

当然,耐压足够的情况下可以稍微减小电容量。

同时也要考虑流过耦合电容的RMS电流

输入电容

SEPIC Ćuk输入端并不是连续的,因此使用这个电源会对前级造成较大的纹波,适当提高输入电容来减小对前级的影响。

电容的耐压考虑一定余量即可。具体计算如下:

输出电容

输出反馈电阻

FB Input Bias Current 50nA-10nA

仿真设计

其实上面的选型大多是国产器件,没有仿真模型,我做的时候也没提前仿真,不过为了完整性这里还是找一个接近的芯片来仿真一下,同时也为了验证一些实际电路我这里不方便做的内容。

由于是先测试了实物后做的仿真,这里预告一下,仿真结果非常接近实测结果,所以拿来验证未测试的项目是有一定可信度的。下面也会和测试波形对比。

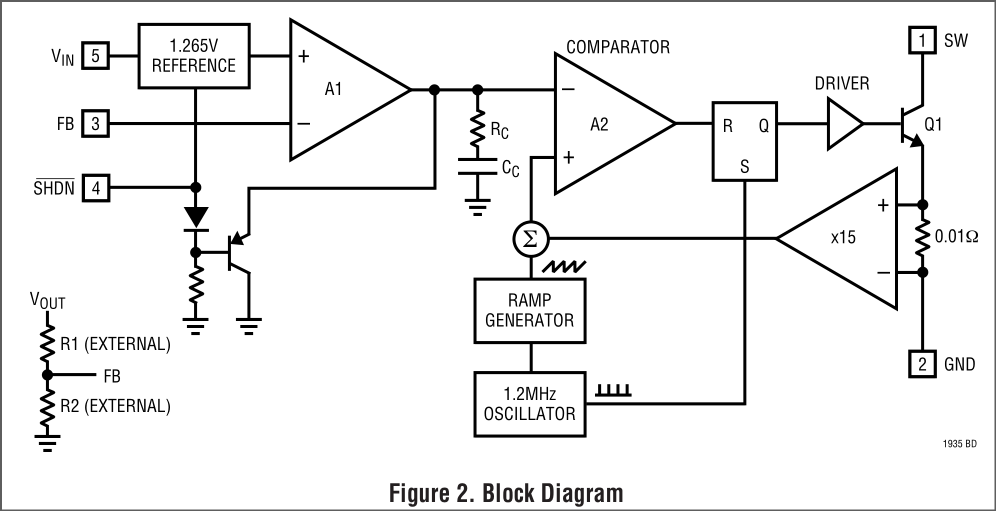

仿真直接用LTspice来做,因为有很完整的电源芯片模型支持,而且容易收敛。这里由于没有MT3608的仿真模型,因此直接找一个类似的BOOST芯片即可。 在ADI选型筛选器中找到小封装的BOOST芯片,这种只有6pin或者5pin的芯片没有补偿引脚,设计结构差不多(我觉得吧),找到两款1.2Mhz,开关限流2A的型号分别为LTC3426(低压)、LT1935.

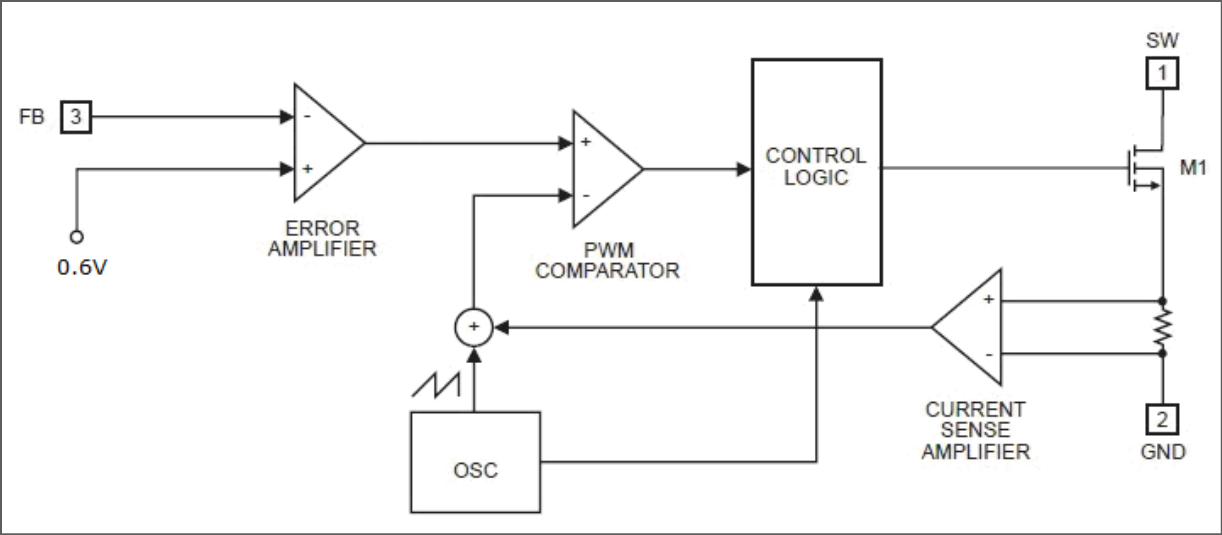

MT3608中的结构图为,手册中指出为peak current mode boost regulator。

LT1935手册中给出的结构图为,手册中指出为constant frequency, current mode control。

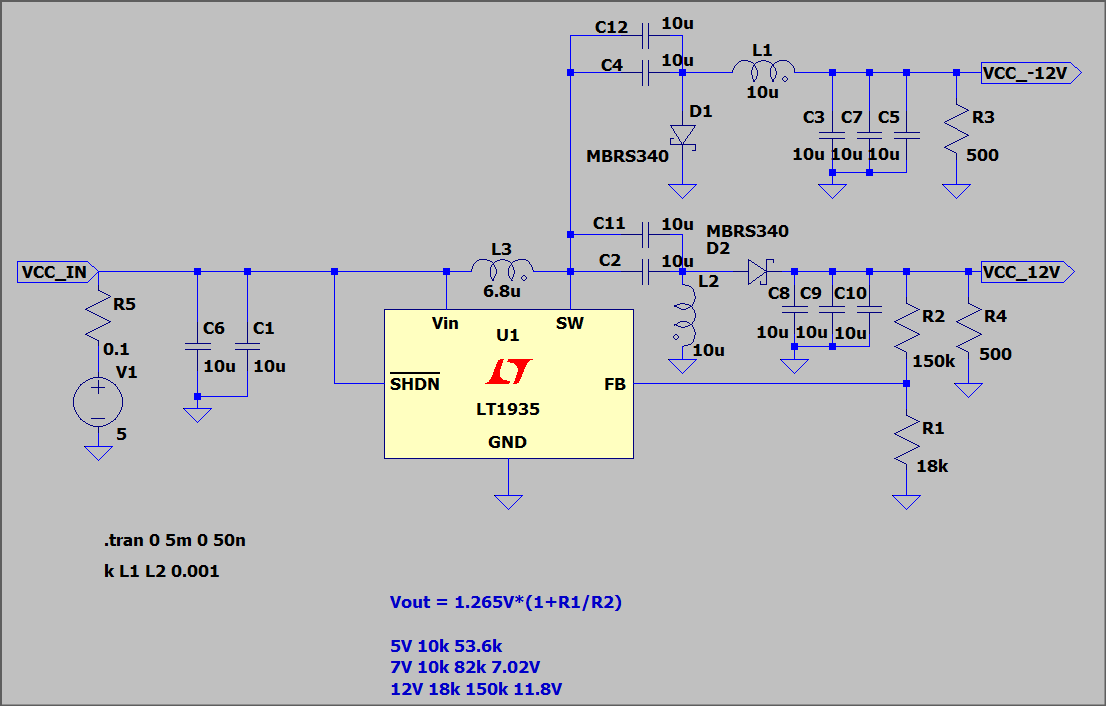

这里直接选用LT1935来进行仿真。 直接上仿真图:

这里为L1 L2添加耦合系数,目前和实物保持一致为两个分立的电感,也可以换成耦合电感。 图中的器件选择LTspice中可选的实际器件的参数,电容包含了ESL和ESR,电感同样包含寄生参数。电阻则选用了理想器件(非理想也没标注其他寄生参数),电源则标记了串联电阻等效内阻。 当前每路输出电流大小为24mA,实际上电感电流这时候还是有不连续的时候,不过为了和实测对上,这里首先展示这种情况下的仿真结果。

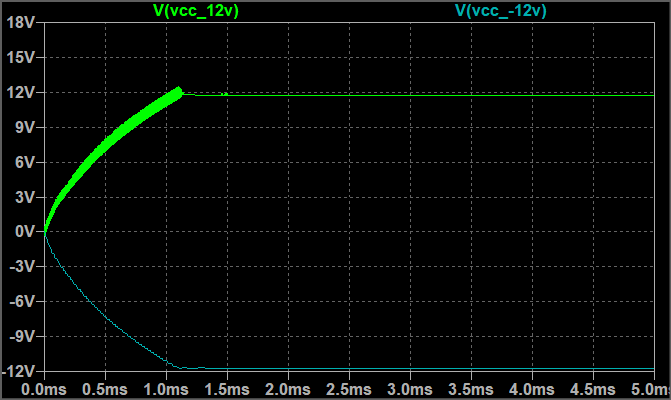

输出波形

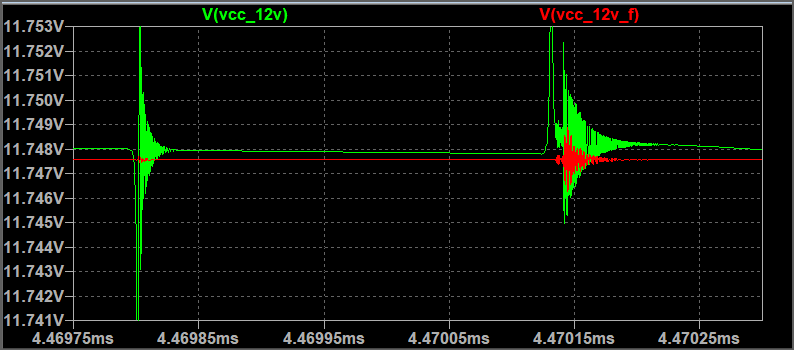

首先看一下输出电压的整体波形。

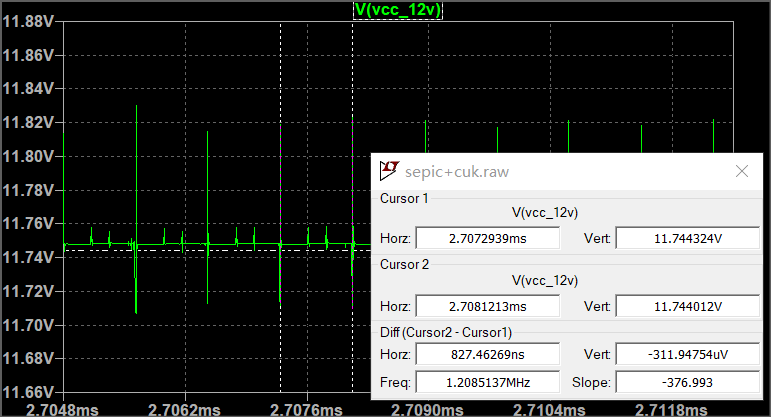

然后看一下正压的细节波形(可以看到开关噪声)

可以看到主要尖峰和开关频率一致,实际上这些尖峰大小和器件的寄生参数以及工作模式有关,如果使用理想器件会看到尖峰更小,或者进入CCM则会看到由于开关电感电流连续这个尖峰也不存在。由于SEPIC输出电流不连续,因此输出具有较大的高次开关谐波分量。

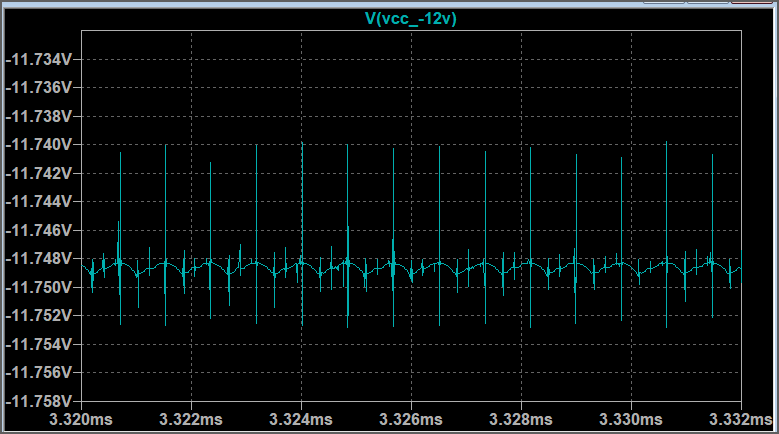

而Ćuk侧输出电流连续,可以看到负压侧细节波形:

同样,由于电感电流不连续导致的尖峰,而其中较为平滑的波形则对应开关纹波。 可以看一下频谱,这些尖峰主要和电感电容的寄生参数有关,后面会解释。

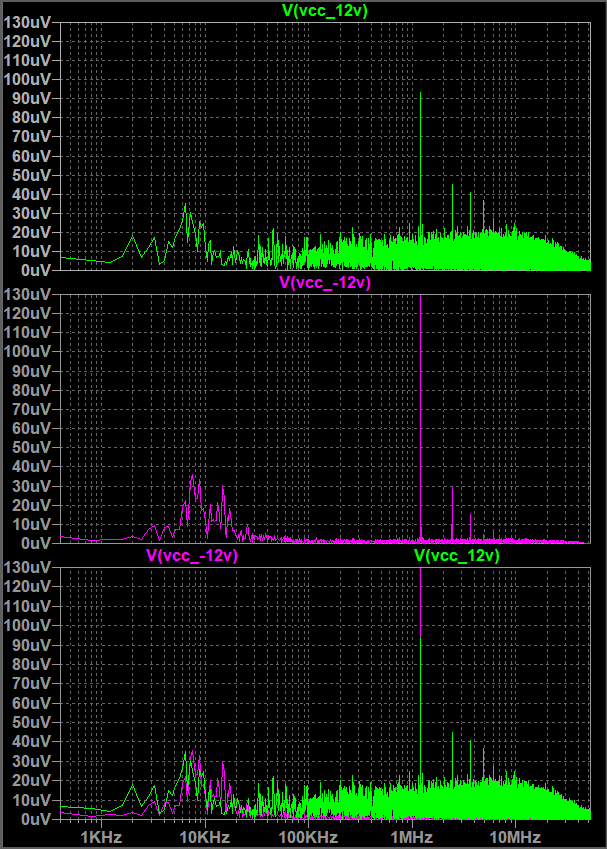

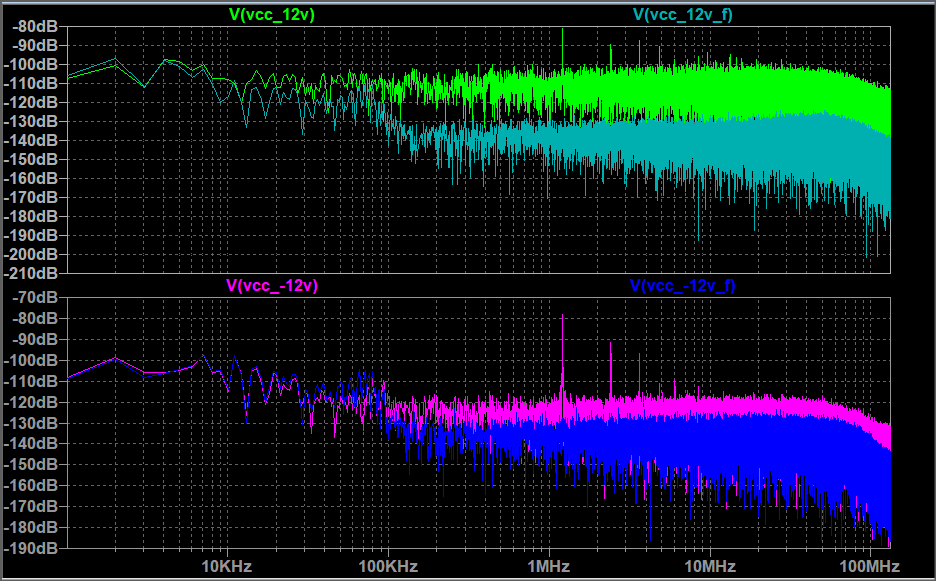

在输出波形这块,最后可以看一下正压输出和负压输出的频谱的对比。(FFT,勾选输出建立后的时间段)

这里可以看到,SEPIC拓扑明显具有更高的高频谐波,而Ćuk侧则相对较为干净,几个开关频点的峰主要来源于电流不连续出现反相电流 感觉是电感的寄生参数的谐振点(我不知道 ) 看adi的 AN 1141中的这个尖峰噪声也不小 达到了150mV 50mV级别 不过可以靠二级滤波来解决

开关节点波形

还是继续上面的测试,这个尖峰很是烦人,在仿真中达到了正压侧100mVpp,负压侧10mVpp,现在看看开关波形。

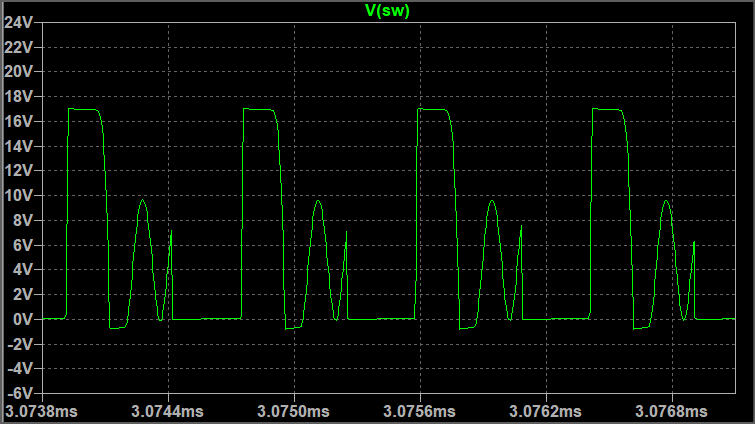

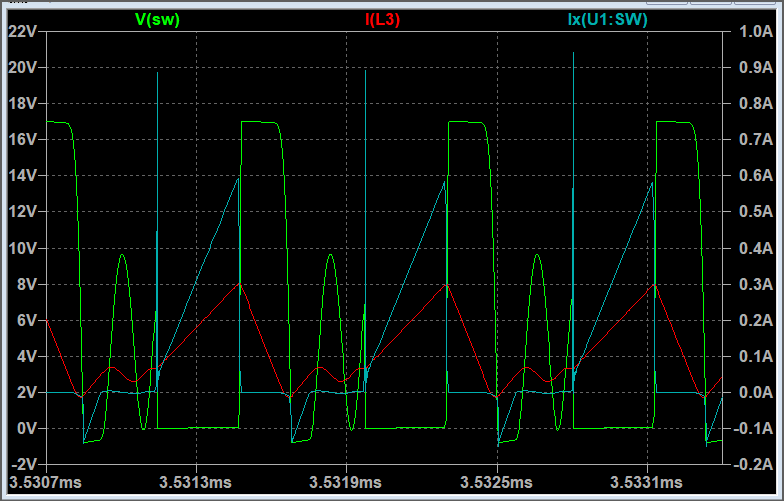

作为对比可以看一下实测板子上开关节点的波形

和预期中的一个完整普通的方波不一样,这个开关节点的电压在完成一个高电平之后,随之而来出现了振荡的波形随后被强制关断到0V. 很明显这里会出现高斜率变化。那么测量输入和开关节点之间的电感上的电流以及SW节点的电流

很明显,占空比比较低,开关控制释放后电感电流一直下降到0,出现了电流不连续点,(是这样吗)和外部的电容一起产生了反方向的电流。

对于这一点,只需要增加负载或者更换具有强制CCM的DCDC芯片,还可以尝试在开关节点增加RC吸收电路(串联RC后并联到开关节点和GND之间),不过后者实际上会增加开关的损耗。这一点会比较难权衡,很难说这种固定模式的简单DCDC芯片能不能瞎折腾。(我不会,仿真下输出优化确实有效但是效率爆炸)。

如果需要优化EMI,减小高频尖峰是一个方法,不过如果本身够用,那么就凑合这么用吧。

而且这种震荡主要和寄生参数有关,如果用理想器件仿真就会发现只有干净的开关纹波而没有尖峰。

而另外,由于电感和电感的寄生并联电容形成高频震荡,输出也就会有高频较高尖峰,可以使用更低寄生参数的器件,可以适当减小电感的值。

输出Π型滤波器设计

如果我们想获得一个更为干净的电源,那么开关电源的输出可以进一步处理。 开关电源输出存在开关频率的噪声,以及由于开关和输入信号混频导致的低频噪声,还有器件本身的内部设计导致的低频噪声。SEPIC输出是不连续的,存在大量开关谐波分量,Ćuk虽然输出连续但是依然要考虑尽量减小输出开关噪声。

当然, 也不要过度设计(过于HIFI),如果后级器件本身的PSRR够用, 那么这里可以减配。例如TL072的PSRR大约80-100dB,对于一般的大信号应用可能已经足够。

情况分析

DCDC转换器的工作频率往往比较高,其开关噪声包含了对应的工作频率和其高次谐波,此次设计中使用的MT3608L标称1.2Mhz,实测1.05Mhz左右。

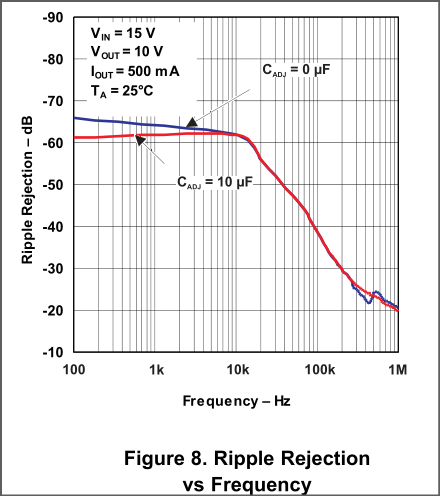

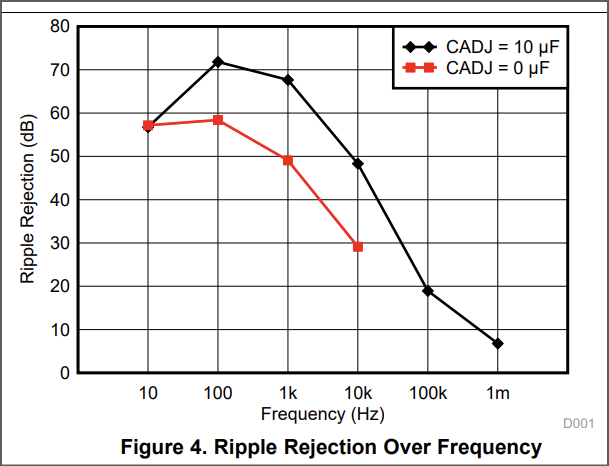

一般的线性稳压器对于较高频率噪声的抑制能力往往会大幅低于低频端。

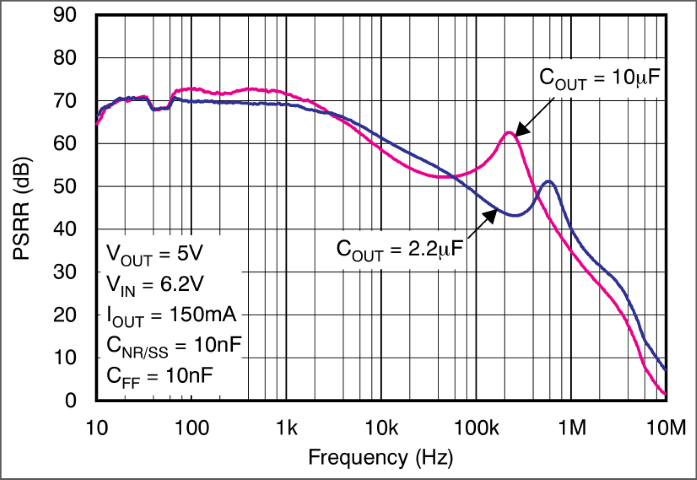

例如TPS7A4901,在

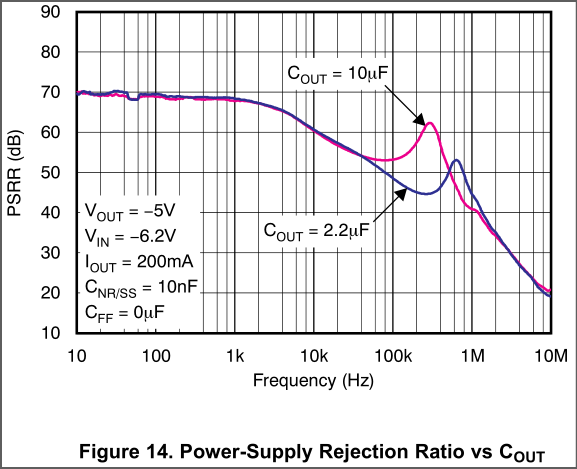

负压的LDO TPS7A3001也差不多,在

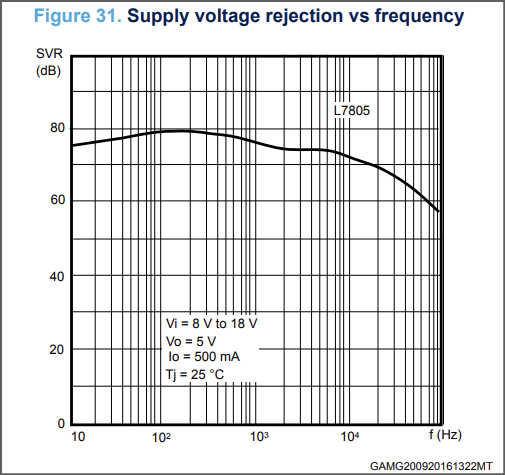

传统的三端稳压器78xx系列只标注了PSRR@120Hz,其值通常在60-70dB左右。而79xx系列的负压线性稳压器的PSRR则稍微低一些,一般为54dB-60dB.

只有120Hz点因为美国电网是60Hz,传统三端稳压器早期主要用于工频变压器输入整流后稳压。只有ST的手册对于78xx给出了PSRR随着频率变化的图,但是似乎完全和他手册里面的写出来的指标对不上,不算保守。而且低频PSRR也太高了,感觉是以前测试方法有些不同出现的。

国产的78L05系列则PSRR更低,只有49dB@120Hz.(你国产的也只标120Hz就离谱)

TI的LM317新手册中给出的PSRR则看起来比较正常,

而LM337的PSRR则给出为

整体上可以看见,这种传统的三端稳压器,基本上最好情况是正压稳压器到1Mhz依然有20dB抑制,而负压可能更低只能到10dB@1Mhz。

不过,地表最强LDO-LT3045的PSRR在1Mhz达到了76dB(对应的负压LDO-LT3094则是74dB@1Mhz).在低频段更是超过100dB. 不过一般应用中,这种超级LDO还是稍微有点贵了。

所以,对于一般应用,不要太指望通过线性稳压器来抑制开关噪声。

Then How to Do ?

不过好消息是,对于PCB路径上的高频噪声,无源滤波器很容易就能实现较好的抑制效果。(这里暂不考虑通过空间辐射耦合到输出端的情况)

考虑一个理想的RC低通滤波器,R=0.23Ω,C=10uF,计算得到的-3dB截止频率为69.23Khz,在1Mhz处的衰减为

计算得到为0.064,即-23.86dB。加上一个传统线性稳压器L7805的抑制效果-20dB,好消息,这已经差不多赶上单个TPS7A49的效果了。

但是仅仅使用RC滤波器,只有一个极点,衰减下降还是不够快,而且电阻也不能加太大否则会有压降,电容增加则会影响瞬态响应,而且成本也会增高。

对于一个10uF 50V耐压的1206封装电容,实际使用中在12V偏压下,只有3uF左右(使用村田仿真工具数据),因此这里电容在体积限制的应用里面也不方便加入太多。

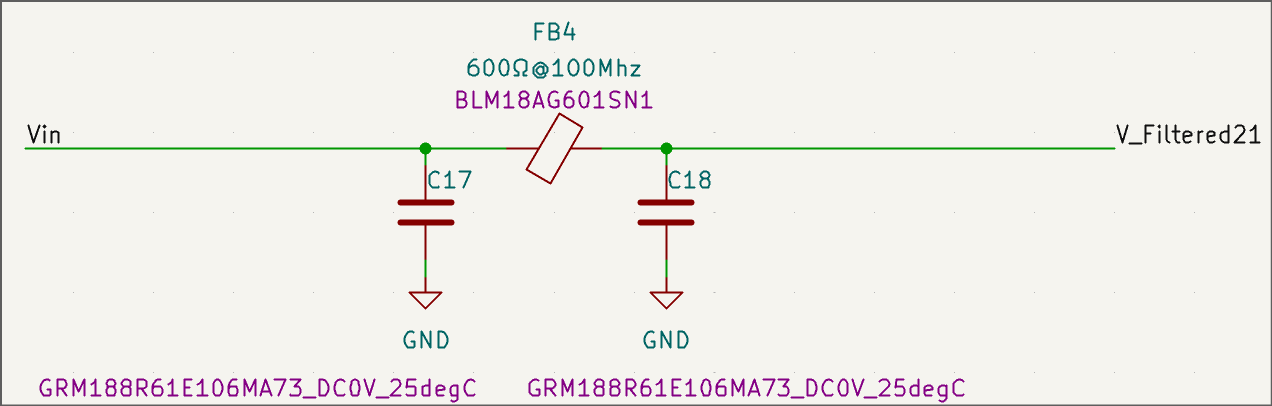

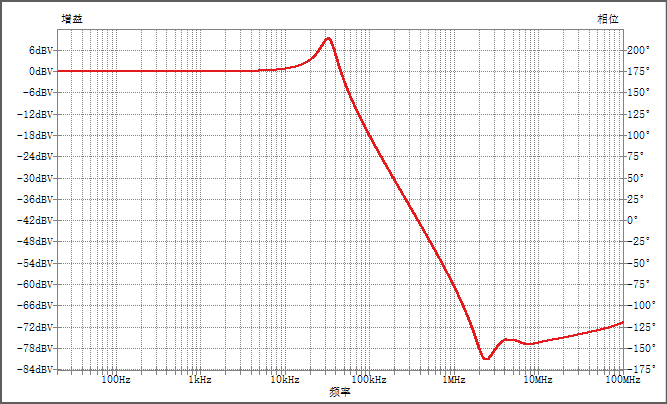

那么如何改善呢?加入电感。 不过,使用单一电感来设计考虑较多(主要是我不会),直接使用磁珠产品更为简单。 下面是使用村田的仿真模型来设计一个Π滤波器,电容为GRM188R61E106MA73,磁珠为BLM18AG601SN1

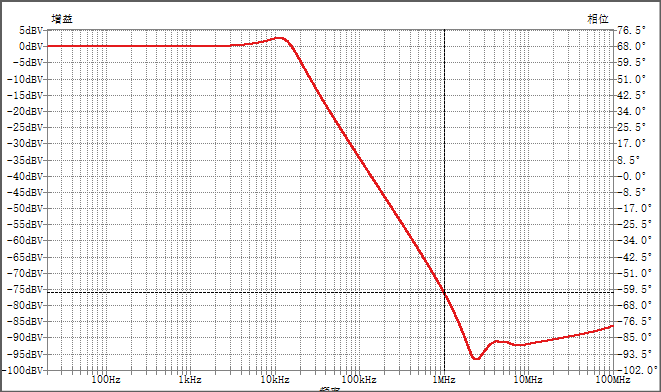

仿真得到的传递特性为

可以看到,使用磁珠的Π滤波器在1Mhz的时候衰减达到了-60dB,不过在30Khz的地方存在尖峰,主要是LC存在谐振点,一般考虑把这个谐振点推到不影响应用的频率处即可,也可以通过增加电容或者换更大阻抗的磁珠来减小谐振峰增益,不过这种方法同时也会改变谐振点,需要权衡考虑是否影响正常工作。如下图增加10uF电容为5个。

当然了,把谐振点推到更低频可以更容易通过LDO来消除这个频率的噪声,也就是如果后级使用现代LDO,对于10Khz级别的噪声已经可以很好抑制了。

不过,顺便一提,在仿真中,Spice模型并没有考虑直流偏压对电容的容量影响,而是取偏压为0V的容量,因此这里实际使用中需要考虑电容的实际容量。

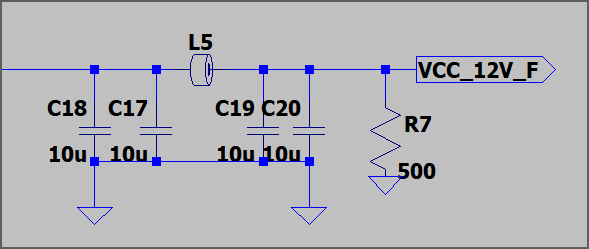

这里下面测试中输出Π型滤波器的磁珠选型为BLM18PG121SN1D,输出电容为10uFx2.

为什么前面仿真中RC滤波的R取值0.23Ω?因为这是上面仿真用到的磁珠的直流阻抗。仿真

接上面的仿真,每路添加添加一个Π型滤波器

测试结果

可以看到,100khz以上的噪声均被抑制,开关噪声已经不再明显。

输出滤波器是否应该放置在环路以内?

https://www.analog.com/cn/technical-articles/designing-second-stage-output-filters-for-switching-power-supplies.html 设计开关电源中使用的二级输出滤波器 这篇文章指出滤波器应该放在环路之中,好处大家都懂,原因是反正就算放在环外也会对环路有影响 ,但是这合理吗?

PSRR

虽然感觉上,开关电源的输出不怎么干净,但是不要忘了他依然是一个稳压器,他具有一定的输入电源纹波抑制能力,只要设计合理,开关电源完全可以让更垃圾的输入电源转换为更符合预期的输出。

这里测不了,只能单独拉一个较差的输入信号和对应的输出信号来展示一下。

一个应用场合是USB VBUS输入,由于各个厂商在PC上整板处理各有不同,USB VBUS的质量一言难尽,对于部分音频应用,就需要改善USB电源质量。

当然,很多情况不需要高于5V的电压,直接使用磁珠滤波加上LDO已经足够使用。实物拍照

这里仅仅做板子展示,各个测试项的连接也都会拍照指出。

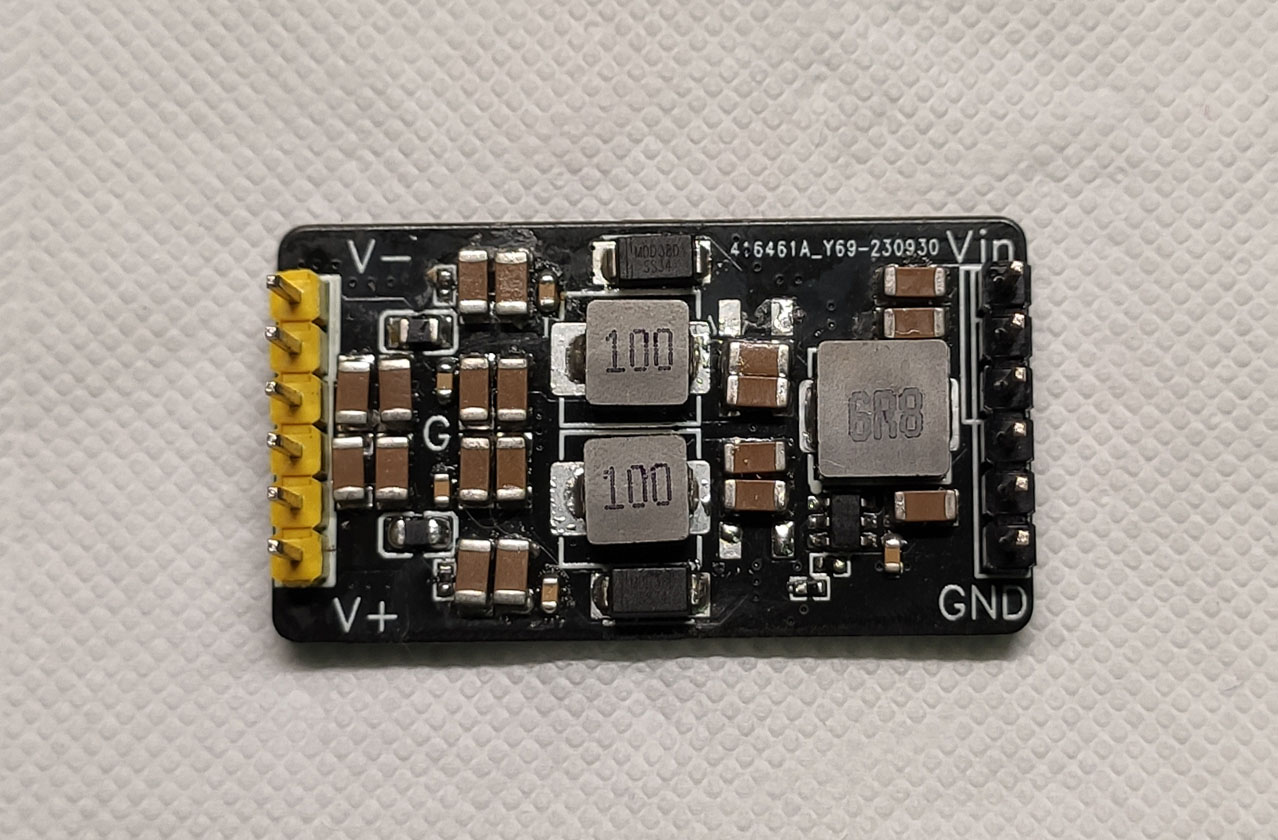

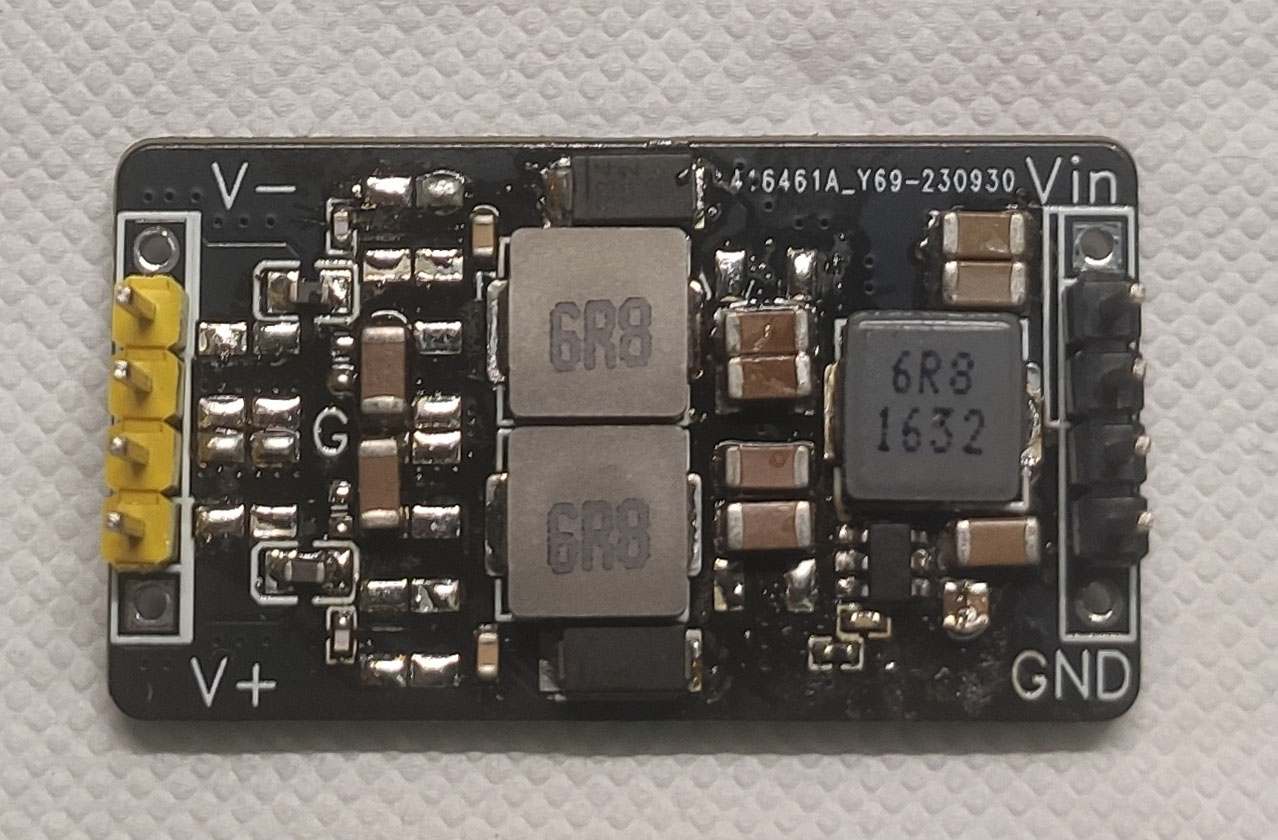

测试板1 这个板子贴全了输出电容,为了能看看这一个板子能做到的效果。

测试板2 这个板子没有输出电容只贴了11uF,磁珠后没有电容,为了验证减配磁珠后电容的效果以及配合LDO是否能做到差不多的效果,同时更换了更小的电感量。不过输入电容量翻倍。

纹波测试

无Π型滤波器输出

有Π型滤波器输出

有Π型滤波器输出(减配电容)

添加线性稳压器输出

减少输出电容+线性稳压器输出

效率测试

负载不对称测试

实际上,负压输出依赖于正压的反馈,因此负压其实是开环输出。

不过对于使用耦合电感的SEPIC+Ćuk电源,由于正负两路的电感耦合在一起,在负载不对称的情况下表现则会更好。

还需要测试但是我没设备了

开关节点波形和电感上的电压波形

电流波形我测不了,没有电流探头。

输出LDO

大多数DCDC芯片的没有使用优化的低频噪声设计,可以很明显看到输出中有低频噪声,这些来源于内部器件 基准的漂移,还有部分来自于输入信号

不过好在这些低频信号通常频率很低,从几百到几K,LDO甚至是传统线性稳压器都可以很轻易消除。

参考文档

Understanding, Measuring, and Reducing Output Voltage Ripple-TI 这个文档详细说明了低频纹波和高频尖峰的来源。

Measuring and Understanding the Output Voltage Ripple of a Boost Converter (ti.com.cn) 这个文章的分析类似。